我們常把晶振比喻為數字電路的心臟,這是因為,數字電路的所有工作都離不開時鐘信號,晶振直接控制著整個系統,若晶振不運作那么整個系統也就癱瘓了,所以好的晶振是決定了數字電路開始工作的先決條件。

現今很多系統晶振時鐘頻率高,干擾諧波能量強;干擾諧波除了從其輸入與輸出兩條走線傳導出來,還會從空間輻射出來,若布局不合理,容易造成很強的雜訊輻射問題,而且很難通過其他方法來解決,因此在PCB 板布局時對晶振和CLK 信號線布局非常重要。

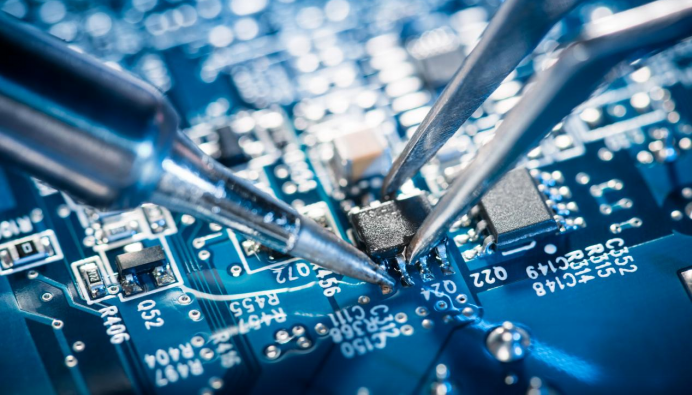

晶振的PCB設計注意事項:

(1) 耦合電容應盡量靠近晶振的電源引腳,位置擺放順序:按電源流入方向,依容值從大到小依次擺放,容值最小的電容最靠近電源引腳。

(2) 晶振的外殼必須接地,可以晶振的向外輻射,也可以屏蔽外來信號對晶振的干擾。

(3) 晶振下面不要布線,保證完全鋪地,同時在晶振的300mil范圍內不要布線,這樣可以防止晶振干擾其他布線、器件和層的性能。

(4) 時鐘信號的走線應盡量短,線寬大一些,在布線長度和遠離發熱源上尋找平衡。

(5) 晶振不要放置在PCB板的邊緣,在板卡設計時尤其注意該點。